Micro-Arch Techniques for Low Power

In the first installment of this series, we emphasized the importance of power optimization and exploration at higher levels of abstraction, where the potential for reducing power consumption is greatest. While fine-grained local changes such as clock gating and operand isolation are well-established for power reduction, there's a need for more substantial alterations at higher levels of abstraction to fully exploit the power-saving potential. Addressing power consumption across logic, memories, and clock networks is paramount, and numerous techniques exist in literature to tackle each category.

What micro-architectural techniques can designers use to explore and reduce power consumption in their designs?

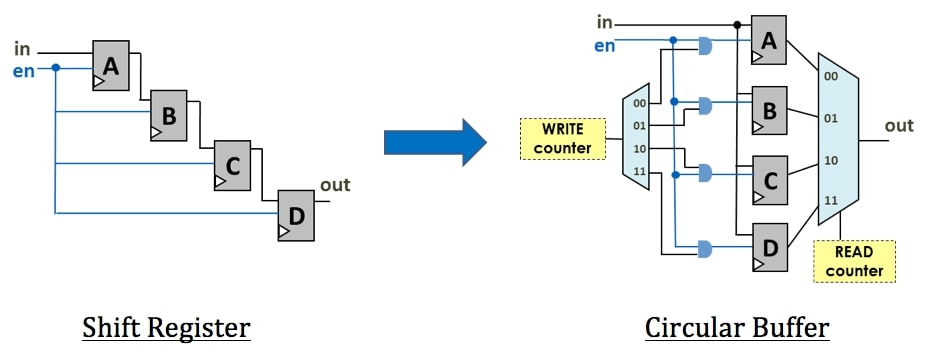

Modifying a Shift Register to a Circular Buffer

A common micro-architectural transformation to minimize power involves replacing shift registers with circular buffers. Shift registers constantly transfer values along a chain of registers as newer values are written in, leading to unnecessary toggles and higher power dissipation. Circular buffers, on the other hand, eliminate the need to move data around the buffer, resulting in significantly lower power consumption. Care must be taken to ensure that the added logic for read/write pointers in circular buffers does not offset the power savings.

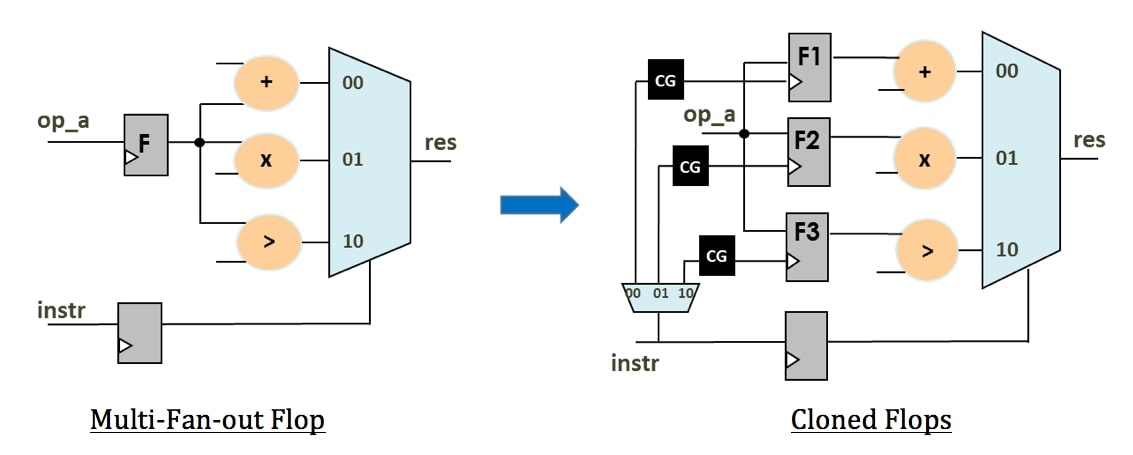

Flop Cloning can create opportunities for clock-gating

Clock gating multiple fan-out flops can be challenging, as at least one of their sinks may be using the value downstream. Flop cloning provides an opportunity to gate multiple operations completely while others are being computed, thus reducing power consumption. This technique involves cloning a flop into multiple instances to control various operations downstream, effectively gating unnecessary toggling and conserving power.

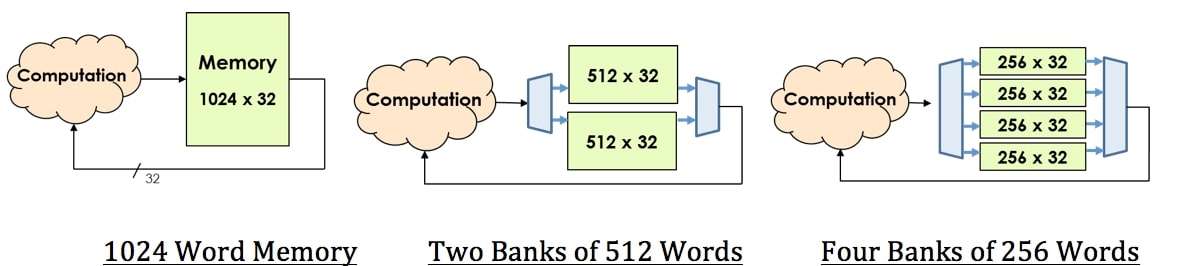

Memory Banking can create memory gating opportunities

Large memories often waste power as only a fraction of the addresses are accessed at any given time. Memory banking divides the memory into smaller banks, allowing designers to shut off inactive banks and save power. By configuring memory from smaller banks, designers can explore different combinations to optimize power consumption. Additionally, exploring different word sizes from a set of memory blocks can further contribute to power savings.

The Challenge of Power Exploration

Despite the availability of various micro-architectural techniques for power optimization, not every designer utilizes them. The lack of precise information about which techniques will yield significant power savings poses a challenge. Designers often lack the necessary insights to determine the potential for power reduction in their designs, leading to suboptimal power-saving strategies.

We need a methodology to streamline design exploration and address the critical bottlenecks in power exploration: quickly identifying applicable techniques and determining associated power savings.