Power Considerations for FinFET Based Designs

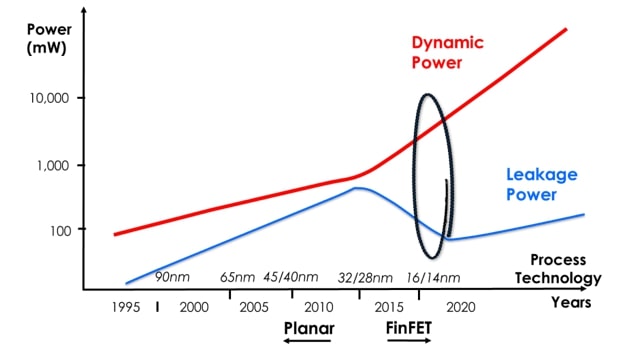

The adoption of finFET technology has brought about a seismic change in the realm of chip design. Not only do finFETs promise enhanced performance within the same power envelope and heightened reliability, but they have also notably curtailed leakage power at smaller technology nodes. However, despite these advancements, the proportion of dynamic power dissipation continues to escalate with the increasing power density attributed to the compacting of more gates at smaller geometries.

What needs to be considered in power exploration in finFET-based designs?

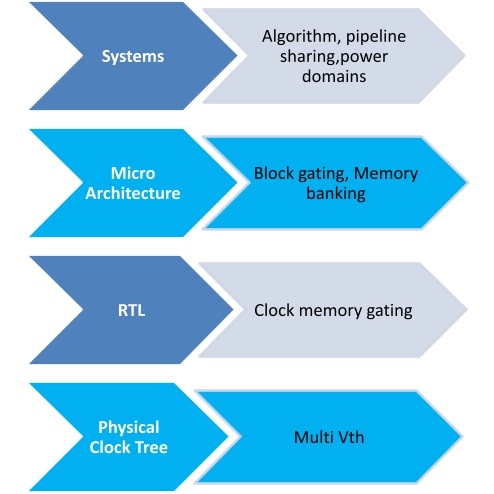

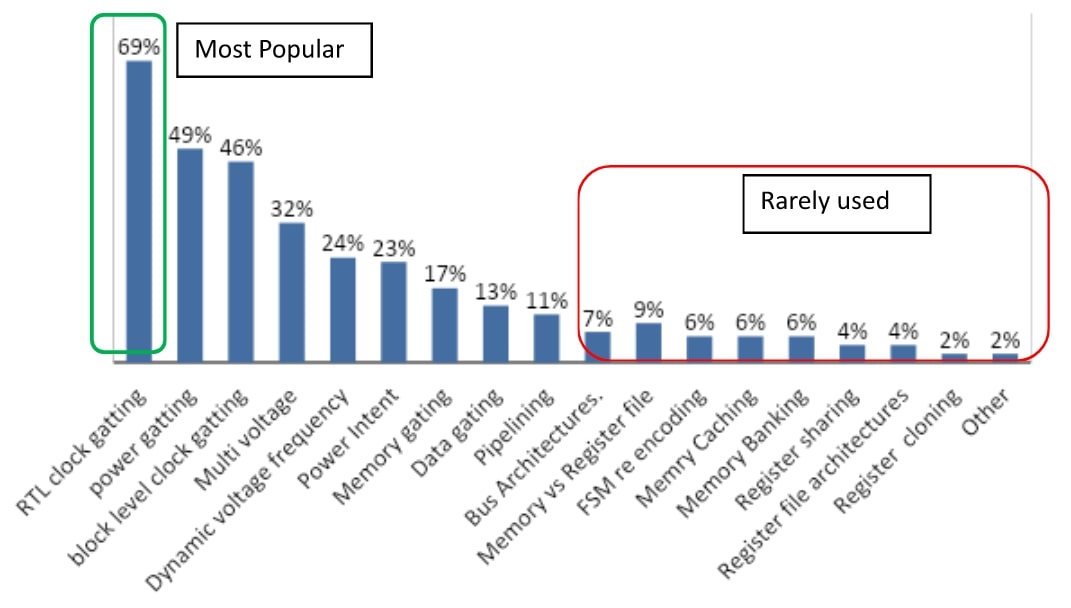

Power optimization in finFET-based designs can be tackled at various levels of abstraction. System-level modifications may involve algorithm alterations, pipelining adjustments, or delineation of power domains. At the microarchitecture level, techniques like block-level clock gating and memory configuration play a crucial role, while clock gating and memory gating are typically deployed at the RTL level. Physical level strategies such as clock tree design and Multi-Vdd, Multi-Vth techniques are employed to further mitigate power consumption. Despite advancements, power reduction efforts often focus on fine-grained techniques like clock gating, neglecting impactful micro-architectural tradeoffs

Interestingly, despite the declining efficacy of fine-grained power-saving techniques like clock gating, power reduction efforts persistently concentrate on later phases of the design process. A recent survey of hundreds of RTL designers indicated a tendency to limit power-saving endeavors to such techniques, possibly undermining the potential for innovation in the low-power market.

Micro-architectural tradeoffs often hold the key to substantial power optimization, yet they are frequently overlooked in power exploration endeavors. Questions such as the optimal memory banking configuration or the potential power savings of replacing a shift register with a circular buffer remain unanswered in many design processes.

Barriers to comprehensive power exploration include a lack of awareness regarding pertinent techniques and the absence of automated tools to evaluate the power impact of potential transformations.

The complexity of power exploration at higher levels of abstraction is formidable. For instance, assessing the power impact of replacing a shift register with a circular buffer necessitates a series of time-consuming steps involving modification of RTL, re-simulation, synthesis, and power estimation

Given the multi-tool and multi-team involvement, the turnaround time for evaluating even a single tradeoff can stretch to several days or weeks, rendering the exploration of multiple tradeoffs nearly impractical.

There is a clear exigency for RTL designers to have access to automated tools for identifying power-saving micro-architectural transformations and facilitating rapid exploration of various implementations. In a separate blog, we will introduce key micro-architectural transformations with significant power-saving potential and outline a methodology for early-stage design exploration.