Achieving <5% Power Correlation with Physically-Aware RTL-PA

Introduction

In chip design, early power numbers are supposed to guide decisions — but what if they’re wrong? One customer found out the hard way: their RTL Power Analysis (RTL-PA) results were telling one story, but after Place & Route (P&R), the numbers doubled.

The mismatch wasn’t just a technical issue — it was a business problem. Teams couldn’t make reliable early optimizations, and surprises arrived late in the flow, when fixes were most expensive.

Challenge

Inaccurate RTL Power Estimation, The core issues were clear:

- Massive Discrepancy: RTL-PA results were 2× off compared to final post-P&R power.

- Root Cause: Without physical layout data, wire capacitance models at the RTL stage were overly simplistic.

- Business Impact: Power optimization decisions were based on flawed data, leading to missed targets and costly late fixes.

Zettabolt Solution

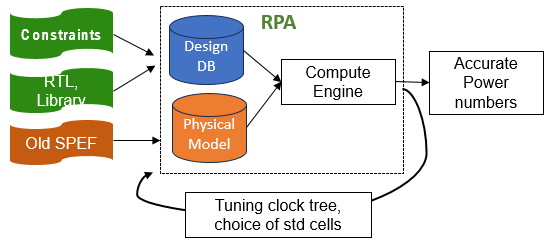

Physically-Aware RTL-PA : Zettabolt introduced a Physically-Aware RTL Power Analysis approach that bridged the gap between RTL and P&R power.

- SPEF-Driven Modeling: Using a SPEF file from a previous design iteration, RPA extracted realistic wire capacitance information at the RTL stage.

- Physical Intelligence Extraction:

- Learned actual standard cell choices and Vth distributions.

- Profiled clock tree structures and buffer/CGIC usage.

- Enhanced Accuracy: These physical insights allowed RPA to model power consumption with near post-layout precision — long before layout was done.

Results

: Accuracy that Drives Optimization <5% Correlation:

- <5% Correlation: RTL-PA numbers now matched post-P&R results within 5%.

- Confident Optimization: With trustworthy early data, the customer implemented impactful RTL changes, including:

- Additional Clock Gating

- Flop Cloning

- Memory Banking

- No More Late Surprises: Power closure was achieved earlier, with fewer costly iterations late in the flow.

Let's Talk